集成电路铝栅CMOS管制造工艺全流程实训

U19E00200

1. 清洗工艺实验

硅片清洗常用物理清洗和化学清洗两种方法。物理清洗主要是刷洗、去离子水冲洗和超声波清洗,去除硅片表面吸附的杂质和颗粒。化学清洗是以酸性、碱性溶液和硅片表面沾污的杂质(如有机物、离子、金属等)发生氧化、络合等化学反应,产生溶于去离子水的物质,再用去离子水冲洗去掉杂质。

去除分子型杂质使用浓硫酸/过氧化氢7:3(体积比)的混合液(3#清洗液)完成。,清洗方法是在125℃温度下,硅片浸泡在3#清洗液中10~20min,使有机物碳化脱附、金属氧化,然后用大量去离子水冲洗。

例如Cu+H2SO4+H2O2=CuSO4+2H2O

氢氧化铵/过氧化氢/去离子水1:1:5混合溶液(1#液)也去除分子型杂质,过氧化氢的氧化作用也可以使有机物碳化脱附,还可以和Cu、Ag、Zn、Ni、Gr等金属离子发生络合反应,生成可溶性的络合物。

例如Cu2+ + 4NH3·H2O = [Cu(NH3)4]2+ + 4H2O

Ag+ + 2NH3·H2O = [Ag(NH3)2]+ + 2H2O

离子沾污因为化学吸附性较强,很难去除,一般使用盐酸/过氧化氢/去离子水1:1:6混合溶液(2#液),在75 ℃ ~85℃温度下浸泡10~20分,去除硅片表面的金属离子、不溶于水的氢氧化物(Al(OH)3、Fe(OH)3、Zn(OH)2),和没有完全脱附的金属杂质。

例如 Fe(OH)3+HCl=FeCl3+H2O

Cu + 2HCl + H2O2 == CuCl2 + 2H2O

硅片的自然氧化层用氢氟酸/去离子水1:50的混合液去除,将硅片浸入氢氟酸溶液中,硅片表面由亲水性变成疏水性,表明硅片表面的二氧化硅完全去除了。扩散工艺产生的硼硅玻璃、磷硅玻璃也可以用这个方法去除。

SIO2+4HF=SIF4↑+2H2O

2. 氧化工艺实验

氧化是氧分子或水分子在高温下与硅发生化学反应,并在硅片表面生长氧化硅的过程。

氧化的温度范围为700—1200℃,氧化层的厚度取决于氧化温度、氧化时间和氧化的方式。氧化温度越高,反应速率越快;相同温度下,氧化时间越长,氧化层的厚度越厚;氧化的方式分为干氧氧化、湿氧氧化和水汽氧化。三种常规热氧化的特点见表 1

表1三种常规热氧化及特点

氧化方法 | 速度 | 均匀重复性 | 氧化性结构 |

干氧氧化 | 慢 | 好 | 致密 |

湿氧氧化 | 快 | 较好 | 中 |

水汽氧化 | 最快 | 差 | 疏松 |

如果需要的氧化层较厚,通常采用干氧-湿氧-干氧的氧化方式。而对于MOS器件的栅氧部分,由于需要的氧化层很薄,又要求质量很好,需要采用干氧氧化的氧化方式。

最后需要说明的是,在硅片表面长一层

薄膜后,由于光的干涉作用,通过肉眼可明显看出颜色变化,氧化层表面的颜色随厚度变化,见表2 。但是氧化层颜色随厚度的增加呈周期性变化。对应同一种颜色,可能有几个不同的厚度,还需要结合具体的工艺条件判断出具体的厚度。此方法只适用于氧化膜厚度在1μm以下的情况。注意,表中所列的颜色,是照明光源与眼睛均垂直于硅片表面时所观测的颜色。

表2 通过颜色的不同可估算SiO2层厚度

颜色 | 氧化层厚度(埃) | ||||

灰 | 100 | ||||

黄褐 | 300 | ||||

蓝 | 800 | ||||

紫 | 1000 | 2750 | 4650 | 6500 | 8500 |

深蓝 | 1400 | 3000 | 4900 | 6800 | 8800 |

绿 | 1850 | 3300 | 5200 | 7200 | 9300 |

黄 | 2000 | 3700 | 5600 | 7500 | 9600 |

橙 | 2250 | 4000 | 6000 | 7900 | 9900 |

红 | 2500 | 4350 | 6250 | 8200 | 10200 |

3. 扩散工艺实验

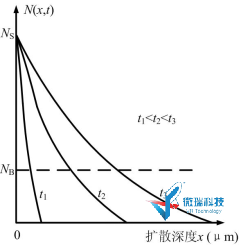

扩散是将一定数量和一定种类的杂质掺入到硅片或其它晶体中去,以改变电学性质。掺入的杂质数量和分布情况都满足要求的工艺过程。扩散是半导体掺杂技术之一。在实际扩散工艺中,扩散需分以下两步完成:首先,在较低温度和较短时间内,在衬底表面预沉积一层高浓度杂质原子。这一步为恒定表面浓度的扩散,扩散深度很浅,目的是得到一固定的掺杂总量,扩散后杂质浓度分布满足余误差分布,见图2.3.1(a);第二步是把预沉积阶段掺入样品表面的杂质在高温下进一步扩散(称为主扩散或再分布),其目的是将杂质推人半导体内部,扩散的温度高,时间长,以控制扩散深度和表面浓度,此阶段近似为有限源扩散。扩散后杂质浓度分布满足高斯分布,见图2.3.1(b)。

(a)恒定表面源扩散浓度分布曲线 (b)有限源扩散浓度分布曲线

图2.2 两种扩散类型的浓度分布曲线

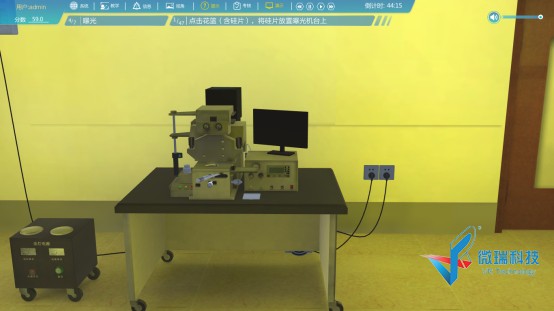

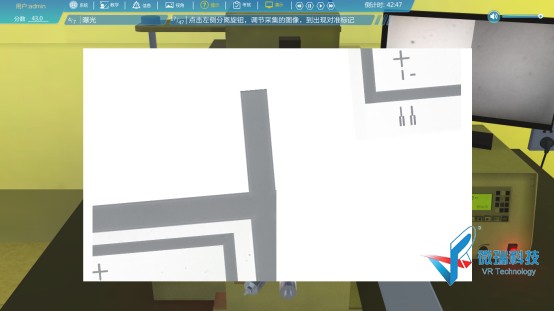

4. 光刻工艺实验

光刻是将掩膜版上的图形经过曝光系统复印在晶圆表面的光敏薄膜上。紫外光透过掩膜版使光敏材料感光而发生光化学变化,产生溶解性不同的区域,再经过碱性物质为主要成分的显影液处理后形成所需图形。

光刻工艺包括正胶光刻和负胶光刻,两种光刻的区别在于曝光区域与未曝光区域的光刻胶和显影液如何反应。正胶光刻是紫外光透过掩膜版,被紫外光曝光区域发生光化学反应后溶于显影液,不透光区域的光刻胶不溶于显影液,仍保留在晶圆表面,形成与掩膜版相同的图形;负胶光刻则是紫外光透过掩膜版,被紫外光曝光区域光刻胶发生交联而硬化,不溶于显影液,不透光区域光刻胶溶于显影液,显影后形成于掩膜版相反的图形。

光刻工艺分为八个基本步骤:表面处理、涂胶、软烘、对准曝光、曝光后烘焙、显影、坚膜和显影后检查。

5. 二氧化硅薄膜刻蚀

在刻蚀反应过程中,有HF电离成H+和F-,其中六个氟离子结合一个硅离子生成六氟硅根络离子(SiF6)2- ,然后与氢离子结合生成氟硅酸(H2SiF6),同时氢离子与二氧化硅中的氧结合生成水,这是典型的酸性氧化物与酸的反应。且反应生成的六氟硅酸在水溶液中可溶性的,因此上式反应平衡向右移动,使得反应不断的进行,因此,根据化学反应式的平衡理论,反应式中的H+和F-的浓度越大,反应的速度就越快。随着反应的进行,溶液中的H+和F-的浓度会不断的下降,结果会导致刻蚀速率的不可控制,以及刻蚀终点的难以把握。因此,为了克服这个缺点,常常采用BOE缓冲溶液代替HF作为二氧化硅的湿法刻蚀试剂,BOE是由HF:NH4F=1:6的成分混合而成,HF为主要的蚀刻液,NH4F则作为缓冲剂使用。其缓冲原理是因为溶液中的NH4F能起着固定〔H+〕的浓度的作用,从而使之保持一定的刻蚀速率,由于溶液中含有大量的F-离子,因此导致电离平衡式向左边移动,即向生成HF的方向移动,从而降低了H+的浓度,而当反应中消耗掉一定量的H+的时候,又会被及时补充,因此缓冲溶液能起着固定H+的浓度的作用,从而保证刻蚀速率的可控。

此外,由于刻蚀速率还受到温度的影响,刻蚀溶液的温度越高刻蚀速率越大,因此本实验采用恒温水浴刻蚀溶液,使得刻蚀反应在恒温下进行,从而达到刻蚀的可控性。

不同致密性结构的二氧化硅,其刻蚀速率则不尽相同,如热氧化生长的二氧化硅分为水蒸汽中氧化和干氧氧化两种,而前者的刻蚀速率则稍快一点。二氧化硅所含的杂质种类及杂质的含量均会影响刻蚀速率,如高浓度的硼会导致刻蚀速率的降低,相反,高浓度的磷会加快刻蚀速率。此外,离子注入产生缺陷会加快二氧化硅的刻蚀速率。

6. 铝薄膜刻蚀

在集成电路制造中,金属铝因为自身的一些优异性能,如电阻率低;能与n+和P+硅以及多晶硅形成欧姆接触;与硅和磷硅玻璃附着性好;此外,铝薄膜易于沉积和刻蚀,几乎常用的CVD、溅射和电子束的方法均能用于沉积铝膜;正是因为这些优点,铝成为集成电路制造的最常用的互联材料。

实验采用磷酸、硝酸、醋酸、和 水体积配比为16:1:1:2的混合刻蚀溶液,在恒定温度为40°的条件下刻蚀金属铝,刻蚀速率可达到100-300nm/min.其中硝酸作为氧化剂用来做提高刻蚀速率,将铝氧化成氧化铝,再用磷酸和水溶解氧化铝。

因此,在反应过程中产生大量的气泡,这些气泡会牢固地附着在硅片表面,并阻止在气泡附着位置的铝的刻蚀,从而造成刻蚀的不均匀性,醋酸就是用来减少这种界面张力从而提高刻蚀的均匀性;此外,在刻蚀过程中进行机械搅拌,减小界面张力;或周期性地把硅片从溶液中拿出也可以使气泡破裂;从而降低这些不利因素。在实际刻蚀操作过程中,正是因为H2气泡的形成和其它的问题,延迟了刻蚀开始的时间或延长了在硅片的所有部位进行完全地开始的时间,因此在刻蚀实验的实际操作中,通常还要加10%~15%的过刻蚀时间以保证完全的刻蚀。

7. 电子束蒸发工艺实验

电子束蒸发是以电子束加热方式,在高真空中电子枪发出电子经系统加速聚焦形成电子束,再经磁场偏转打到坩锅的成膜材料上加热,并使之变成气态原子沉积到硅片上的物理过程。在蒸发镀膜真空室内,电子束直接聚焦在蒸发材料表面,获得很高的能量密度,使难熔金属、不分解化合物、合金等材料熔化蒸发,产生蒸气,在真空腔内气压小于10-2Pa的情况下,蒸发源气体分子或原子不会环境气体发生碰撞,以直线运动的方式抵达基片表面,沉积成为薄膜。被蒸发材料放在冷坩埚中,避免了其他部分材料的蒸发,能得到更纯净的沉积薄膜。

实验内容:

1) 使用电子束蒸发台淀积200nm的铝薄膜。

2) 显微镜观察铝薄膜表面形貌。

3) 使用膜厚仪测试膜厚。

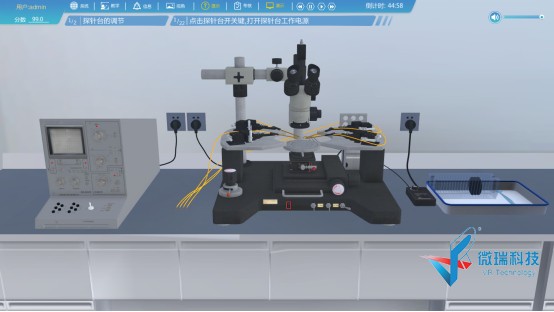

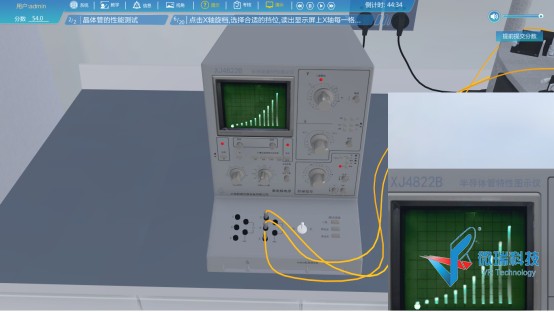

8. 晶圆级MOS管性能测试实验

对晶圆级MOS管进行测试,测试内容主要包括输出特性、转移特性以及耐压特性,下面以NMOS晶体管为例分别说明。

1)晶圆级MOS管的输出特性

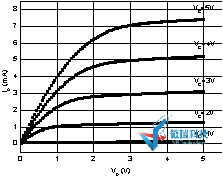

将晶圆级MOS管的漏、栅、源分别接入晶体管图示仪测试台上的C、B、E接入孔中进行测试。如图3.17所示是晶圆级NMOS管的一组输出特性曲线,此时晶体管的源极及衬底接地信号,栅极为电压输入信号VG,VG是一级一级的阶梯波信号,漏极电压VD的变化范围是0-5V,不同的栅极电压信号VG对应了不同的漏极电流信号ID。

|

|

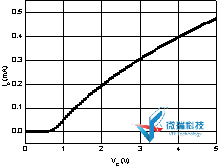

2)晶圆级MOS管的转移特性

在获得晶圆级NMOS管的输出特性曲线的基础上,将晶体管图示仪上的集电极电压旋档旋转至阶梯波图标处便可以得到晶圆级NMOS管的转移特性曲线。如图3.18所示,由所有VG条状线的上端点构成了一条曲线,即转移特性曲线,通过这条曲线可以读取晶体管的开启电压Vt值。

|

|

图 3.18晶圆级NMOS管的转移特性曲线

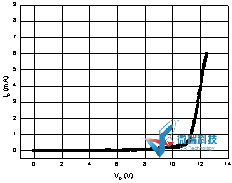

3)晶圆级MOS管的耐压特性

耐压能力是衡量MOS管性能好坏的一项重要指标,如漏源耐压、漏与衬底的耐压以及栅耐压等。本实验主要讲解晶圆级NMOS管的漏源耐压BVDS特性。测试BVDS时首先需要将NMOS管的栅极与源和衬底连接在一起,然后缓慢的扫描集电极电压,直到观察到击穿现象,击穿点对应的电压就是BVDS。

|

|

图3.19 晶圆级NMOS管的漏源耐压特性曲线

上一篇:集成电路三极管制造工艺全流程实训

售前咨询专员

售前咨询专员